May/June 2019

FACULTY OF ENGINEERING

First-Year Examination for the Degrees

of

Bachelor and Master of Engineering

EENG14000 DIGITAL CIRCUITS AND SYSTEMS

Logic Design

Tick all the right choices. There is at least one correct choice. To get the full mark for each multiple choice question, all correct choices must be ticked. If a wrong answer is ticked the mark for the question will be zero even if all correct choices are ticked. There is no negative marking for wrong answers. An unattempted question will score zero.

From QA.1 to QA.24: Correct answers will be marked with +1.

From QA.25 to QA.28: Correct answers will be marked with +4.

QA.29 and QA.30: Correct answers will be marked with +5.

If you change your mind about an answer, redraw new empty boxes and tick the boxes you want.

QA.1) Any combinational logic function can be represented with:

o a list of Maxterms.

o NAND logic operators only.

o a list of minterms.

o AND and NOT logic operators.

QA.2) Digital systems are composed of:

o a network of transistors behaving like switches.

o a network of transistors not behaving like switches.

o logic gates.

o none of the above.

QA.3) A sequential digital system can be represented with:

o a state transition table.

o a truth table.

o state diagram.

o a list of minterms.

QA.4) A combinational digital system can be fully described by a:

o Moore machine.

o Mealy machine.

o state diagram.

o none of the above.

QA.5) A digital system based on sequential logic circuits may contain:

o D latches.

o a clock signal.

o a state register.

o D flipflops.

QA.6) To minimise a Boolean expression we could use:

o Karnaugh maps.

o the truth table.

o transition table.

o none of the above.

QA.7) When an N-digit positional number system with a radix (base) R is used, what is the weight of the least significant digit if the number has 4 digits situated at right hand side of the radix point (assuming N > 4)?

o R-N+4 .

o R-N-3 .

o R-4 .

o R-3 .

QA.8) When an N-digit positional number system with a radix (base) R is used, what is the weight of the most significant digit if the number has one digit situated at right hand side of the radix point?

o RN-1 .

o N-1 .

o R-1 .

o none of the above.

QA.9) The sum of the two natural binary numbers (111101)2 and (000010)2 is:

o (111110)2 .

o (011011)2 .

o (011111)2 .

o none of the above.

QA.10) The sum of the two signed-magnitude binary numbers (01010)2 and (00101)2 is:

o (10111)16 .

o (11111)2 .

o (01111)2 .

o overflow.

QA.11) The subtraction of the two’s-complement binary numbers (11111)2 - (00100)2 is:

o (11100)2 .

o overflow.

o (00011)2 .

o (11011).

QA.12) The sum of the two’s-complement binary numbers (1000)2 and (1011)2 is:

o (1011)2 .

o overflow.

o (0011)2 .

o none of the above.

QA.13) The following two’s-complement number

(111111111111111111111111111111111111111111111111111111)2 is equivalent in decimal to:

o 1 in two’s complement.

o 11 in two’s complement.

o 0.

o none of the above.

QA.14) 103F can be a number of the number system:

o binary.

o hexadecimal.

o octal.

o decimal.

QA.15) Convert to hexadecimal the following natural binary number (000100110011)2 :

o (F03)16 .

o (E13)16 .

o (123)16 .

o (133)16 .

QA.16) The following two’s-complement binary number (10000) is equivalent to:

o (-8)10 .

o (7)10 .

o (-16)10 .

o (15)10 .

QA.17) Multiplying by 8 the natural binary number (00011)2 , results in (assuming result stored in 6 bits):

o (000110)2 .

o (110000)2 .

o (011000)2 .

o (001100)2 .

QA.18) Dividing by 8 the two’s-complement binary number (111000)2 , results in:

o (111110)2 .

o (111100)2 .

o (000110)2 .

o (111111)2 .

QA19) In which binary number system do we have an overflow in the following addition, (01000)2 + (11110)2? Assume that the result of the sum is stored in a 6-bit word:

o Signed-magnitude binary.

o Unsigned binary.

o Two’s-complement binary.

o None of the above.

QA.20) Which bit-word corresponds to one positive or negative increment from the following Gray code 00110:

o 11100.

o 10000.

o 10110.

o 01100.

QA.21) Consider a binary floating point representation with a Mantissa of 3 bits and an Exponent of 3 bits. Assuming normalisation of mantissa and hidden bit techniques are used, what is the maximum decimal number that can be represented if the Exponent is fixed at 001?

o 1.9375.

o 0.9375.

o 1.875.

o 3.75.

QA.22) A 16-to-1 multiplexer must have:

o 3-bit word signal to route the input data to the output.

o 4-bit word signal to route the input data to the output.

o 2-bit word signal to route the input data to the output.

o none of the above.

QA.23) A one bit full-adder:

o uses a certain amount of XOR gates.

o performs a logic shift.

o performs a cyclic shift.

o none of the above.

QA.24) Which positional number system can be converted to binary using the substitution method?

o hexadecimal.

o octal.

o A number system with N digits such that N=2M +1.

o decimal.

QA.25) Consider the following Boolean function S = (A .B)’ + C. Select any logic circuit that realises the logic function S:

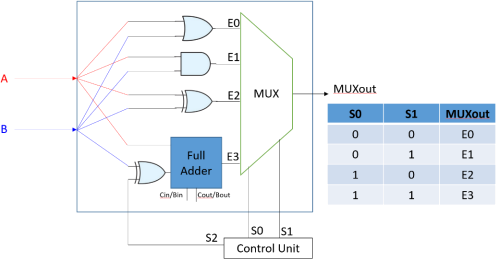

QA.26) Observe the following 1-Bit ALU in Figure 1. What values S0, S1, and S2

should be set to by the Control Unit to perform A XOR B logic operation:

Figure 1: 1-Bit ALU

o S0 S1 S2 = 0 1 0

o S0 S1 S2 = 1 1 0

o S0 S1 S2 = 0 1 1

o S0 S1 S2 = 1 0 1

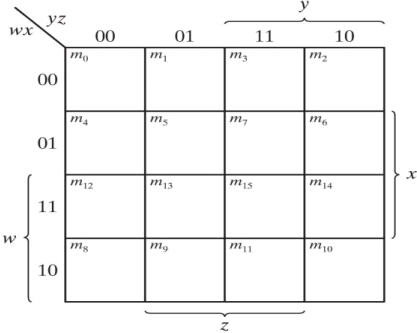

QA.27) Minimise F= ![]() W,X,Y,Z(2,6,14,10) then select the resulting simplified Boolean

W,X,Y,Z(2,6,14,10) then select the resulting simplified Boolean

expression. Feel free to use the following Karnaugh map in Figure 2 (use of Karnaugh map not marked):

Figure 2: Karnaugh map.

o F = w’ + y

o F = x + z

o F = z’ + y

o F = z + y’

QA.28) Minimise F= ΣW,X,Y,Z(0,2,4,6,8,10,12,14) then select the resulting simplified

Boolean expression F’. Feel free to use the following Karnaugh map in Figure 3 (use of Karnaugh map not marked):

Figure 3: Karnaugh map.

o F’ = y’

o F’ = y

o F’ = z

o F’ = z’

QA.29) Consider the following behaviour of input signals A, B, and C of the circuit below in Figure 4 (see Appendix D-latch page10):

Figure 4: Circuit diagram and inputs behaviour.

Ignoring propagation delay issues, during the period of time starting just after t1 and ending just before t2, if the output QN is initially High, the output Q:

o changes from Low to High.

o changes from High to Low.

o changes from High to Low then from Low to High.

o None of the above.

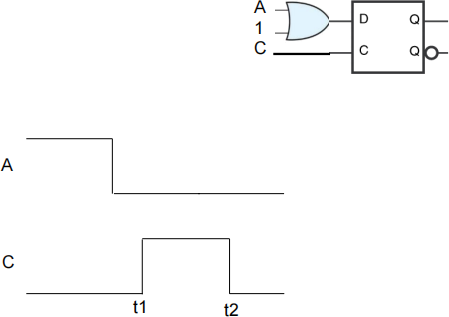

QA.30) Consider the following behaviour of input signals A and C of the circuit below in Figure 5 (see Appendix D-latch page10):

Figure 5: Circuit diagram and inputs behaviour.

Ignoring propagation delay issues, during the period of time between t1 and t2, if the output Q is initially High, it:

o changes from High to Low then Low to High only.

o changes from High to Low then Low to High then High to Low only.

o stays High all the time.

o changes from High to Low only.